This article is more than 1 year old

HPE, IBM, ARM, Samsung and pals in plot to weave 'memory fabric'

Everyone but Intel and Cisco working together to build storage-class memory

A group of suppliers have got together as a consortium to develop Gen-Z - a scalable, high-performance bus or interconnect fabric linking computers and memory.

The Gen-Z consortium is an open, non-proprietary, transparent industry standards body. It says it believes open standards provide a level playing field to promote adoption, innovation and choice.

Consortium members are AMD, ARM, Broadcom, Cavium Inc, Cray, Dell EMC, Hewlett Packard Enterprise (HPE), Huawei, IBM, IDT, Lenovo, Mellanox Technologies, Micron, Microsemi, Red Hat, Samsung, Seagate, SK Hynix, Western Digital Corporation and Xilinx.

See anyone missing? Yup, it's the monopoly data centre and server CPU supplier Intel. Curious that. Especially as its XPoint-developing buddy, Micron, is a member. Any other missing candidates? Cisco's not present and, as a UCS server supplier, we might think it had an interest in CPU-memory fabrics.

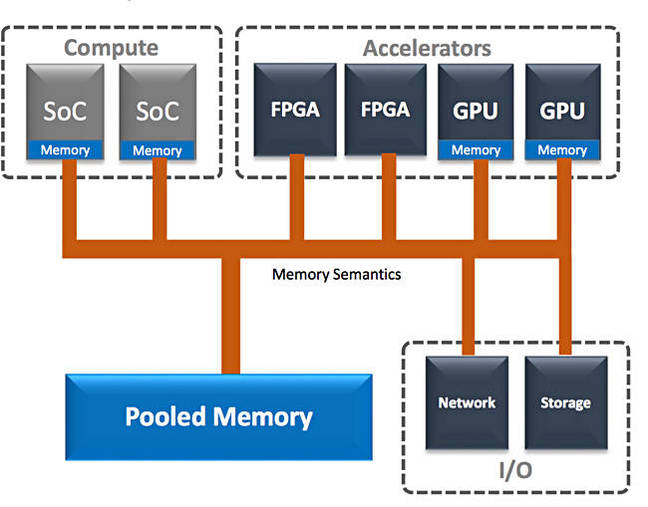

Gen-Z need for pooled memory concept sl-de

We're told "this flexible, high-performance memory semantic fabric provides a peer-to-peer interconnect that easily accesses large volumes of data while lowering costs and avoiding today’s bottlenecks." It's meant to enable storage accesses to be closer to memory accesses in speed through the use of storage class memory and new programmatic and architectural ideas.

A memory semantic fabric handles all communication as memory operations, such as load/store, put/get and atomic operations typically used by a processor. Memory semantics are optimal at sub-microsecond latencies from CPU load command to register store. This is unlike storage accesses which are block-based and managed by complex, code intensive, software stacks.

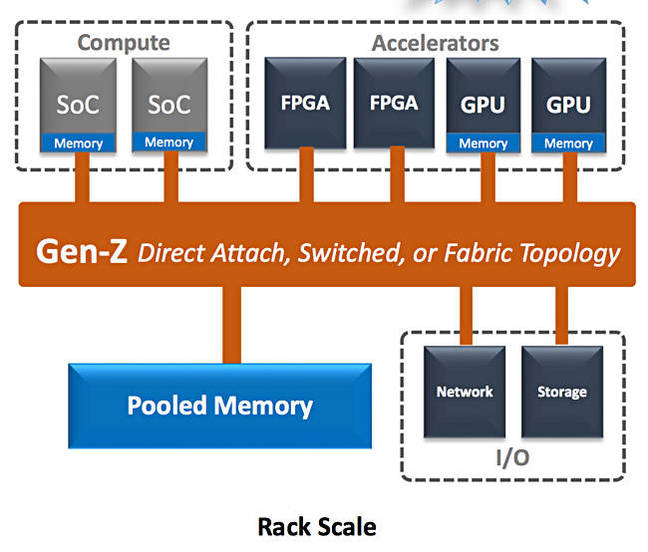

The consortium's announcement release states: "The emergence of low latency, storage-class memory, and demand for rack scale resource pools require a new approach to data access."

Its background thinking is that memory tiers will become increasingly important, and rack-scale composability requires a high bandwidth, low latency fabric which must seamlessly plug into existing ecosystems without requiring OS changes.

It provides three general Gen-Z interconnect characteristics:

- High bandwidth and low latency through a simplified interface based on memory semantics, scalable from tens to several hundred GB/sec of bandwidth, with sub-100 nanosecs load-to-use memory latency,

- Supports scalable memory pools and resources for real-time analytics and in-memory applications,

- Highly software compatible with no required changes to the operating system,

- Scales from simple, low cost connectivity to highly capable, rack scale interconnect.

Gen-Z fabric concept

The core specification, covering the architecture and protocol, will be finalized in late 2016, and the Gen-Z consortium is accepting new members. We might see first products appearing in 2017.

There is a briefing slide deck here (pdf). ®