This article is more than 1 year old

Oracle outlines Ellisonized Sparc roadmap

Data barely presented

Questions unanswered

Maybe this was a generic performance statement and the future Sparc-based "engineered systems" will do even better. Fowler did not stick around and answer questions after his presentation, and the panel of thirteen experts on the instant message feed didn't answer a single direct question of import posed by Webcast attendees.

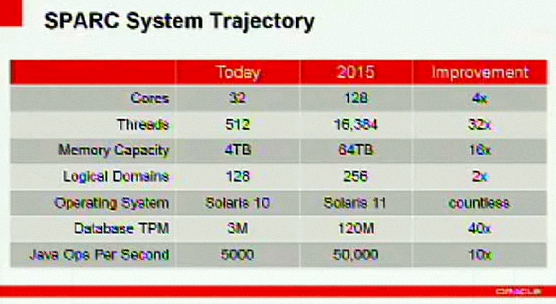

The table below was a little easier to understand, and lays out the Sparc plan in a general way.

Fowler said that today's Sparc-based machines top out at 32 cores with 512 threads and can address 4TB of main memory, have 128 logical domain partitions, support about 3 million OLTP transactions per minute, and perform about 5,000 Java operations per second. (These Java figures do not appear to be any of the SPEC Java tests.)

Those are not the feeds and speeds of the current Sparc Enterprise M9000 server using Fujitsu's quad-core Sparc64-VII processors, however, and neither are they not the feeds and speeds of the Sparc T5440 server using Sun's own SparcT2+ chips. It appears that the specs of a four-socket machine using the forthcoming "Rainbow Falls" Sparc T3 processor, which will have 16 cores with eight threads each, running at 1.67GHz if the old Sun roadmap from June 2009 is still holding.

The current Sparc T5440 server uses an eight-core processor that yields only 256 threads in four sockets and supports only 512GB of main memory — and it surely cannot do 3 million transactions per minute on any OLTP test that is generally used by server vendors.

Though the boost coming from the Sparc T3 will be welcome to Sun's customer base, even this future machine is not exactly big iron, but instead a high-end midrange box or a low-end enterprise box. Fowler went for an easy compare to make the numbers more dramatic looking ahead.

The current Sparc Enterprise M9000 uses 2.88GHz processors, scales up to 256 cores in a single system image, supports up to 4TB of memory, and has 24 dynamic hardware domains (a more static partition than the LDoms that are used on the Sparc T series processors). Neither Fujitsu nor Sun have done OLTP tests on big SMP Sparc iron in many years, although to its credit, Oracle did a TPC-C test Oracle ran on a Sparc T5440 cluster last year. So it is hard to say how many TPMs a Sparc M9000 could do — but it is safe to say several millions and more than even a Sparc T3-based system could do.

Looking out to 2015, Fowler said that Sun can deliver a server with 128 cores with a stunning 16,384 threads that will be able to support 64TB of main memory, host 256 logical domains, and run Solaris 11, which is tuned to handle all those threads and that main memory. This box will be able to crank through 120 million TPMs on OLTP workloads — forty times that Sparc T3 machine — and do 50,000 Java operations per second — ten times that Sparc T3 box. (If Fowler was indeed pre-announcing that Sparc T3 box with a wink and a nod, as I suspect.)

If you look at the blurry Sparc systems roadmap at the top of this story, it looks like this future Sparc machine from 2015 will span 64 sockets. The other graphic tells us that it will have 128 cores, so that makes the future Sparc chip a dual-core processor — if I'm reading that blurry page right. When you do the math, that works out to 128 threads per core, which sounds insane. But then again, so did eight threads per core and eight cores per chip a few years back on the Sparc T2+ chips.

And the definition of a "core" could get pretty fuzzy over the next five years, too, with some elements of a what used to be a core being shared across the computing elements in novel ways to reduce redundancies and power consumption. AMD, for example, is blurring the distinction between core and chip with its future "Bulldozer" family of cores —- and I use that word loosely, as one must.

The interesting bit about that future Sparc platform for 2015 is that it doesn't say either T Series, which is the Sun design, or M Series, which is the Fujitsu design. Perhaps Fujitsu and Oracle are going to co-develop whatever this future Sparc processor and server platform is, and perhaps Oracle, which has plenty of cash, is going to go it alone as it always intended to do with its 16-core "Rock" UltraSparc-RK SMP processors, which were killed off last June.

On the system roadmap at the top of this story, the T Series update slated for 2010 is the Rainbow Falls update, which will double up the cores and the performance of the T Series platform. The M Series update is the 3GHz Sparc64-VII+ upgrade, called the "Jupiter-E" by Fujitsu, which is due this year, just like Rainbow Falls. The Jupiter-E is a quad-core chip with two threads per core, just like its 2.88GHz predecessor.

From Cascade Falls to T Series

The T Series family gets an upgrade in 2011, and this looks like the chip that was formerly known as "Yosemite Falls" inside of Sun. This T Series chip was originally expected to have eight cores and eight threads per core, but to run at a faster 2.5GHz clock speed. The Yosemite Falls chip was expected to have a new core design and be implemented in a 40 nanometer process, like Rainbow Falls.

The T Series upgrade in 2013 looks like the chip project from inside Sun formerly known as "Cascade Falls," which is a rev on Yosemite Falls that puts 16 cores (eight threads each) on a chip, which is implemented in a 28nm process; the Cascade Falls chips were designed for servers that scale from one to eight sockets in a single system image.

The M Series upgrade in late 2012 and on the next upgrade at the cusp of 2013 and 2014 (if this roadmap is to scale) are a bit of a mystery. It is reasonable to guess that 2012 will see another crank on the clock with a process shrink to 40 or 45nm from Fujitsu — call it the Jupiter-F — and maybe a clock speed on the order of 4.5GHz without much changing except cache sizes and perhaps an integrated L3 cache.

The machine in late 2013 or early 2014 could be based on a variant of the eight-core, 16-thread Sparc64-VIIIfx chip, code-named "Venus," that Fujitsu is making for the Project Keisoku 10 petaflops supercomputer.

Whatever Oracle and Fujitsu are doing, Fowler and his team were not going to actually disclose it today. Oracle and Fujitsu are negotiating at the moment, with Fujitsu president Masami Yamamoto saying back in June that he expected a deal right about now.

Fowler did not say much about Oracle's x64 server business, except that it would do rack and tower machines, and that it would certify its software on other boxes, singling out Dell and HP for their renewed Solaris OEM agreements. Fowler said nothing about AMD Opteron chips and the fact that Oracle has killed them off in its x64 product line —- at least for now, and possibly as a negotiating tactic, as it did to get whatever concessions it wanted out of HP for its Solaris OEM agreement.

Bootnote: Oracle's systems roadmap presentation is now online here. ®