This article is more than 1 year old

Intel's Tri-Gate gamble: It's now or never

Deep dive into Chipzilla's last chance at the low end

Deep – really deep – inside Tri-Gate

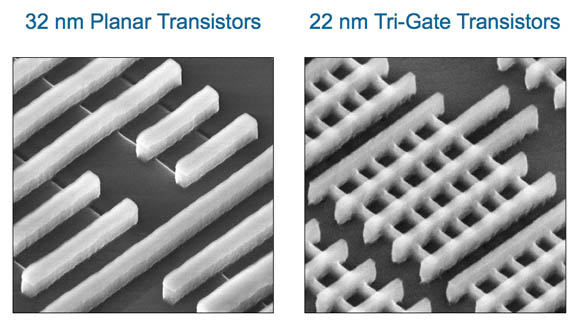

As we mentioned earlier, Tri-Gate is a variation of the FinFET concept, in which instead of lying below the gate as in a traditional planar transistor design, the charge-carrying silicon pokes up into the gate itself.

In a planar design, gates were lain across a flat silicon substrate – not 3-D enough for marketeers, however.

This non-planar construction, by the way, is why you'll hear Intel marketeers exalting the Tri-Gate design as "3-D". Well, yeah, that's not entirely untrue, but the gate-wrapped fin is hardly 3-D enough to warrant such buzz-lines as this one from the Wednesday presentation: "Transistors have now entered the third dimension! – and, yes, that's Intel's italics and Intel's exclamation point.

In any case, you might reasonably ask: "So the fin sticks up in the gate? So %$#@!ing what?" Bohr's answer to that perfectly reasonable question is equally reasonable: "The key advantage of this structure – and it comes from the fact that the gate wraps around this fin – [is that] it provides fully depleted operation of the transistor."

Bohr's answer, of course, is only reasonable if you know why a fully depleted transistor is a good thing – which takes a bit of background to explain.

When a traditional microprocessor transistor is in the "on" state, current flows from source to drain through what's called the transistor's "inversion layer", which interacts in Intel's designs with the transistor's high-k metal oxide interface with the gate. That's all well and good.

However, when the transistor is in the "off" state, some charge can still trickle through the silicon substrate. When it does, the transistor is regarded as not being fully depleted. That's bad.

When voltage hangs around like this, it degrades what chip boffins call the "sub-threshold slope" of the transistor – which Bohr defined as "essentially the transistor turn-off characteristics," or which we can think of as how "off" the off state actually is.

When the transistor's off state is fully depleted, it helps minimize power usage. Also, a fully depleted transistor can have a lower threshold voltage – meaning that the voltage needed to switch it from off to on can be lower, again saving power.

"When you operate at a lower threshold voltage," Bohr explains, "you have improved performance. Or you can operate at lower voltage, and if you operate at lower voltage, there's a significant active-power saving – and that's really probably the most important advantage of Tri-Gate."

So, a fully depleted transistor both leaks less power and requires less power. All good.

Planar processors are hell to make fully depleted. In their traditional state, there's a lot of room in the silicon substrate to house errant voltages. You can, however, add an oxide insulator below the source and the drain to create what's called a partially depleted silicon-on-insulator (PDSOI) design.

You can go all the way to fully depleted (FDSOI) without going FinFET by depositing an extremely thin SOI layer on top of the oxide – but reaching full depletion this way is quite expensive. According to Bohr, baking a chip this way adds at least 10 per cent to the total wafer cost.

Tri-Gate, by comparison, is cheap. "Another nice thing about the Tri-Gate devices," Bohr says, "is that they're not that expensive to add. Compared to a planar version of 22 nanometers, Tri-Gate transistors add only about 2 to 3 per cent cost to the finished wafer."

The Tri-Gate way of reaching full depletion is to stick that silicon fin up into the gate, have the inversion layer on both sides and the top of the fin, with the high-k metal oxide of the gate snug against the inversion layer. Presto – no room for nasty voltages to accumulate, plus the larger wrap-around inversion layer and metal-oxide interface allow for more current, and thus better performance. Bonus!

Another nifty Tri-Gate trick is that you can have multiple fins in the same transistor: more fins, more current, better performance. Or, as Bohr puts it succinctly: "You can gang together these fins to create larger transistors with higher drive currents."

This "How many fins do you want?" capability will help Tri-Gate to populate throughout Intel's product line, from low-power single-fin transistors to multi-fin structures that will find their way into Xeons – and even into Itaniums, when that benighted chip reaches its Kittson incarnation, two generations from today's 9300 series.