This article is more than 1 year old

ARM specs out first 64-bit RISC chips

Punching Intel, AMD in the server jewels from below

The ARM RISC processor is getting true 64-bit processing and memory addressing - removing the last practical barrier to seeing an army of ARM chips take a run at the desktops and servers that give Intel and AMD their moolah.

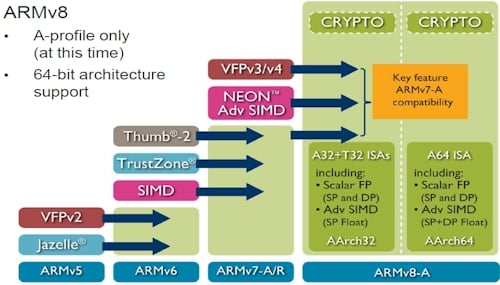

At the ARM TechCon conference in Santa Clara on Thursday, the top brass at ARM Holdings, the company that controls the core designs and licenses them to a slew of chip makers for modification in smartphones, tablets, and other embedded devices, showed off the new ARMv8 architecture. It's an incremental improvement over the current v7 architecture, just like the 64-bit extensions to the original 32-bit x86 processors from Intel and AMD were.

The new ARMv8 architecture has two execution states, the AArch32 state that is compatible with prior generations of 32-bit ARM processors, and AArch64, the new 64-bit extensions. At the moment, the ARMv8 architecture has only been profiled for what ARM calls the A line of its Cortex reference designs, which means they are designated for application processing such as that done on smartphones and tablets – and within a few years PCs and servers, if Intel can't smash the ARM collective with its prowess in chip fabrication technology.

There will presumably be Cortex-M designs extended to 64-bit for embedded processors as well as Cortex-R designs, which are aimed at throughput intensive real-time uses.

The ARM RISC processor roadmap for applications

The ARMv8 architecture will bring forward TrustZone virtualization (which debuted with the ARM v6) and NEON SIMD instructions, which debuted with the ARM v7 designs. The interesting thing about the ARMv8 is that it will offer both double-precision floating point math through that NEON unit.

ARM started work on its 64-bit architecture back in 2007, as you can see from this technical presentation. The quad-core Cortex-A15 designs, which are the most advanced ones that ARM has done, have 32-bit processing, but a 40-bit virtual addressing scheme. That 40-bit virtual addressing scheme allows for clever programmers to get beyond the 4GB physical memory addressing of the 32-bit ARM chips. But having a clean 64-bit design means that companies that have created code to run on 64-bit x86, Itanium, Power, Sparc, or MIPS processors will have an easier time porting their code over to ARMv8 chips.

In his presentation, Richard Grisenthwaite, the lead architect at ARM, said that the company was seeing "strong partner interest in 64-bit" but that it was still some years away from "must have" status.

This is not what the server vendors and hyperscale datacenter customers El Reg talks to are saying. In fact, many say that until ARM is 64-bit, it is not a chip that they can adopt in PC or server designs – or that customers will buy. In any event, while the ARMv8 chips support 64-bit processing, which means up to 16 exabytes of memory, the virtual address space is topped out at 48-bits right now.

While ARMv8 processors will be able to encode and decode AES encryption, and will support on-chip acceleration of the SHA-1 and SHA-256 hashing algorithms too. Another big change – and one required for servers – is that the ARMv8 chips will have a finer grain of exception levels between the TrustZone hardware partitioning on the chip, a virtual machine hypervisor, and the operating system than is possible with the ARM v7 designs.

There are four exception levels, and each gets their own handler and thread stack options. ARM Holdings will release detailed specifications for the ARMv8 A profiles in the second half of 2012 and expects prototype systems from vendors in 2014 based on its reference designs.

Intel has a lot of time to make Atom a better chip, and AMD still has time to do whatever it is going to do. ARM needs to move faster – or AMD will. ®