This article is more than 1 year old

Flash DOOMED to drive itself off a cliff - boffins

NAND to hit endurance, reliability limits

Microsoft and University of California San Diego researchers have said flash has a bleak future because smaller and more densely packed circuits on the chips' silicon will make it too slow and unreliable. Enterprise flash cost/bit will stagnate and the cutting edge that is flash will become a blunted blade.

The boffins presented their findings in a paper [PDF] at the Usenix FAST'12 conference in San Jose. They wanted to see how process size shrinkage and the increase in data density - expressed as the number of bits per cell - affected the performance of the NAND and, perhaps, lessened its differential from hard disk drives in terms of performance, reliability and endurance.

They collected data about 45 flash chips from six manufacturers, spanning feature sizes from 72nm to 25nm, and looked at raw flash chip data with assumptions made about a controller-managed Flash Translation Layer (FTL) which adapts a file system o it's suitable for memory chip hardware.

Then they looked at performance measurements as the flash feature size was reduced, and wrote: "We use this analysis to predict the performance and cost characteristics of future SSDs. We show that future gains in density will come at significant drops in performance and reliability."

Here's their main assertion:

While flash density in terms of bits/mm2 and feature size scaling continues to increase rapidly, all other figures of merit for flash – performance, program/erase endurance, energy efficiency, and data retention time – decline steeply as density rises.For example, our data show each additional bit-per-cell increases write latency by 4X and reduces program/erase lifetime by 10X to 20X, while providing decreasing returns in density (2X, 1.5X, and 1.3X between 1-,2-,3- and 4-bit cells, respectively).

As a result, we are reaching the limit of what current flash management techniques can deliver in terms of usable capacity – we may be able to build more spacious SSDs, but they may be too slow and unreliable to be competitive against disks of similar cost in enterprise applications.

The researchers say: "Increasing flash’s density by adding bits to a cell or by decreasing feature size reduces both (a) lifetime and (b) reliability."

Flash on the ropes

Yes, well, we know this. It's well understood that every process size reduction lowers performance, endurance and reliability. All the researchers have done is wrap statistics around these raw flash chip bones. They take data about 45 raw chips and extrapolate it it to see what the future will bring. The researchers say they "construct an idealised SSD model that makes optimistic assumptions about the efficiency of the flash translation layer (FTL)".

Then: "To model the effect of evolving flash characteristics on complete SSDs we combine empirical measurement of flash chips in an SSD architecture with a constant die count called SSD-CDC. SSD-CDC’s architecture is representative of high-end SSDs from companies such as FusionIO, OCZ and Virident. SSD-CDC manages an array of flash chips and presents a block-based interface. The SSD’s controller implements the FTL."

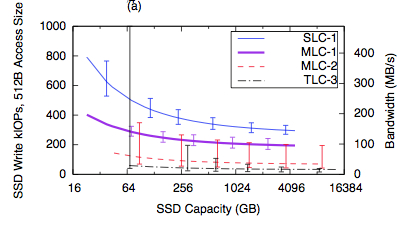

Flash write IOPS extrapolation

The results for "future projections for seven metrics of SSD-CDC: capacity, read latency, write latency, read bandwidth, write bandwidth, read IOPs and write IOPs" are shown in complex graphs full of standard deviations and error bars showing the range probability. We show one above as an example, dealing with 512B write IOPS with single-level cell (one bit per cell), multi-level cell (two bits per cell) and triple-level cell (three bits per cell) flash and a capacity range from 16GB to 16,384 GB

A cloudy flash future

The researchers' overall conclusion is:

SSDs will continue to improve by some metrics (notably density and cost per bit), but everything else about them is poised to get worse. This makes the future of SSDs cloudy: While the growing capacity of SSDs and high IOP rates will make them attractive in many applications, the reduction in performance that is necessary to increase capacity while keeping costs in check may make it difficult for SSDs to scale as a viable technology for some applications.

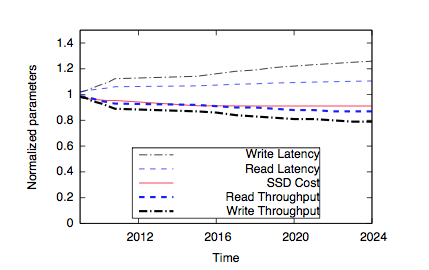

Flash with normalised parameters

A final chart (above) using normalised parameters, shows that "while the cost of an MLC-based SSD remains roughly constant, read and particularly write performance decline. Our projections show that the cost of the flash in SSD-CDC will remain roughly constant and that density will continue to increase (as long as flash scaling continues as projected). However, they also show that access latencies will increase by 26 per cent and that bandwidth (in both MB/sec and IOPS) will drop by 21 per cent".

4-bit-per-cell NAND: no way

Drilling into the research, it appears the boffins are saying that 4-bits-per-cell flash won't ever appear in enterprise storage without revolutionary technology advances. Secondly, they are setting the scene for post-NAND technologies, such as HP's memristor, STT-RAM, phase-change memory, other resistive RAM technologies and IBM's racetrack memory. All these combine NAND's non-volatility with elements of DRAM speed and endurance.

The researchers' findings illustrate why suppliers are pouring money into post-NAND technology developments. In terms of increasing flash density, NAND technology is going to come to a pretty abrupt stop at the 3-bit MLC, 19-10nm process stage. Getting beyond either of those limits will produce slow, short-life SSDs that aren't any cheaper.

Data storage requirements are not going to stop increasing and servers' needs to access that information fast aren't going to go away either. Something has got to give and it will be NAND technology giving way to its successor, whatever that will be. ®