This article is more than 1 year old

3D processor-memory mashups take center stage

'I have seen the future, and it is stacked'

Real apps, real benchmarks

Georgia Institute of Technology's "3D-MAPS: 3D massively parallel processor with stacked memory": The team behind the 3D-MAPS processor went one step beyond the IBM and UoM's chips by creating a processor that performed real, benchmarkable work.

After rattling off a list of processor/memory-mashup research papers, 3D-MAPS team member Sung Kyu Lim of the Georgia Institute of Technology told his ISSCC audience that he had been unable to find another team that had been able to build a prototype that could be programmed to handle actual workloads.

"I am very happy to say that we accomplished that goal," Lim said.

3D-MAPS's silicon was fabricated by GlobalFoundries at 130nm, and layer-to-layer bonding and TSV technology was provided by Tezzaron Semiconductor, which has its design engineering and sales center in Naperville, Illinois, and process design and manufacturing in Singapore. The chip runs at 1.5 volts and consumes up to 4W, resulting in a power density of 162 watts per square centimenter.

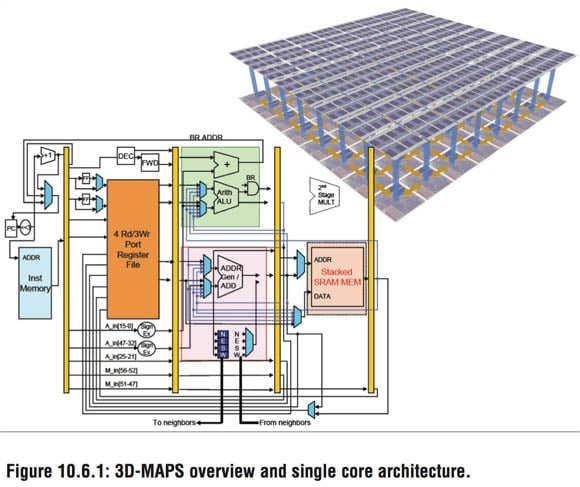

Like the Centip3De, 3D-MAPS has 64 cores. Unlike the Centip3De's ARM Cortex-M3 cores, however, 3D-MAPS has 64 VLIW (very long instruction word) cores of the team's own devising, each running at 277MHz.

Lim described the design of the cores as "not full-fledged." There's no floating-point unit, for example, just one five-stage arithmetic pipeline and one data-memory pipeline that can sustain one 4-byte data memory operation per clock cycle. Each core is hooked up to 4KB of "scratchpad" SRAM – the memory isn't globally shared; each core has access only to its own scratchpad.

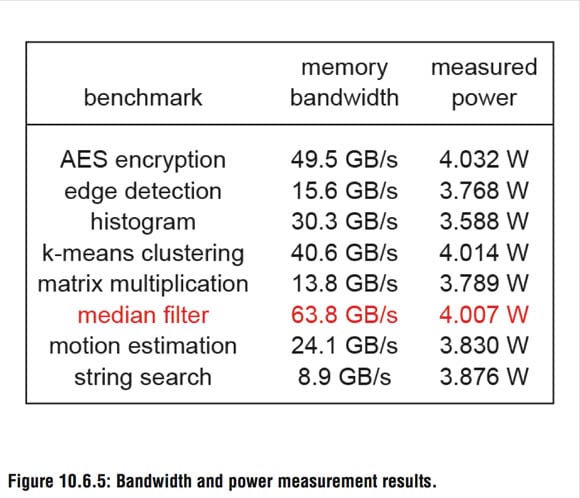

Lim said that in one of the benchmarks that 3D-MAPS ran – a median filter test – memory bandwidth came in at a hair below 64 gigabytes per second. The team claims that at the 277MHz clock rate, the memory bandwidth will theoretically max out at 70.9GB/sec.

As might be expected, different tasks performed on 3D-MAPS have different performance profiles

The cores are connected "neighbor to neighbor," Lim said. "We wanted to have a network on the chip, but we didn't have time to finish it."

Part of that time pressure, no doubt, was due to the fact that according to Lim there are no commercial 3D-chip CAD tools on the market – he and his team had to write their own scripts and plug-ins for existing 2D tools such as Encounter from Cadence, PrimeTime from Synopsys, and others.

That said, version two of 3D-MAPS – dubbed, appropriately, V2 – has already been taped out, and should be ready by next year's ISSCC or sooner. V2 will have 128 cores, 256MB of DRAM and 512MB of SRAM, and other improvements, such as using TSVs not just mainly for IO but also for communicating with DRAM.

When 3D-MAPS V2 appears, there'll likely be more to hear about IBM's 3D efforts, the seven-layer Centip3De shoud have appeared, and undoubtedly other efforts will come to fruition, as well.

ISSCC 2013 may very well be 3D processors' debutante ball. ®

* Update

The University of Michigan's David Fick emailed us to correct our comment on throttling smaller-process chips down to near-threshold voltages. "Those numbers (45MHz for 45nm, and 110MHz for 32nm) were for the voltage scaled cores," he writes. "We have an ARM Cortex-M3 operating at 750MHz in another 45nm chip, which is how the 45MHz number was estimated. 32nm was based on simulation."

He also added a bit of info on future steps planned for the Centip3De project. "I'd like to also mention that Centip3De will be able to run the same sorts of benchmarks that 3D-MAPS can run," he writes, "but we need to have the DRAM to do it (hopefully coming later this year). We use a commercial core, which allows us to use a C++ compiler, etc, but we are just a bit short on memory space."