This article is more than 1 year old

Better late than never: Monster 15-core Xeon chips let loose by Intel

New mission-critical CPUs are mission-critical to Chipzilla's critical money-making mission

Intel's long-reigning top dog in the x86 server market, the Xeon E7 "Westmere-EX" of April 2011, can finally enjoy a well-deserved retirement: its "Ivy Bridge–EX" replacement, prosaically named the Xeon E7 v2 series, has finally arrived.

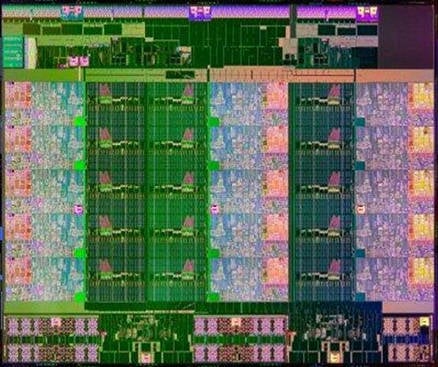

Count the compute cores on this Xeon E7 v2 die – notice anything, well, odd?

When the Westmere-EX Xeon E7 chips were released oh so long ago, it seemed reasonable to assume that their follow-on would be a "Sandy Bridge–EX" Xeon series, seeing as how the Sandy Bridge microarchitecture was the next "tock" in Intel's "tick-tock" cadence of following a new process technology tick with a new microarchitecture tock.

Didn't happen. In September 2012, Intel told The Reg that it would skip the 32nm iteration of its Xeon E7 v2 processors based on the "Sandy Bridge" microarchitecture. Instead, Chipzilla would use that same basic microarchitecture, but bake it using the 22nm, Tri-Gate Ivy-Bridge process technology.

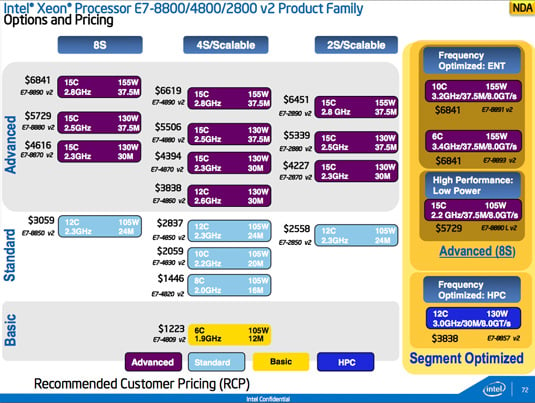

Intel had said that these "Ivy Bridge–EX" Xeons would appear in the fourth quarter of last year. They didn't – but now they're finally here, and available in three series: the two-socket E7-2800, four-socket E7-4800, and eight-socket (you guessed it) E7-8800.

From what Intel performance marketing spokesman Frank Jensen told us, the new versions of the Xeon E7 v2 series should be worth the wait, with an average 2x performance improvement over their predecessors. Note that what Jensen said is not "up to 2x" but an "average of 2x", citing the performance of the new top-of-the line four-socket Xeon E7-4890 v2 in a series of benchmarks against the former top-dog Xeon E7-4870.

Save your pennies

Before we dip into some of the details of this new chippery, do know that these babies are far from impulse buys. When we were briefed on their impending availability last month, the highest-priced 15-core Xeon E7 v2s were projected to run a cool $6,841. Prices may have changed by Tuesday morning's rollout, but don't bet on it.

Intel's top-drawer E7 v2 Xeon costs as much as 20 3.5GHz quad-core Core i7-4770Ks (click to enlarge)

Sharp-eyed Reg readers may have thought they caught a typo in that last paragraph. But no, the E7 v2s with the highest core counts do have 15 cores – an odd number of cores, indeed (pun intended) – arranged in three ranks of five cores each with base (pre-Turbo) clock rates of 2.2GHz to 2.8GHz.

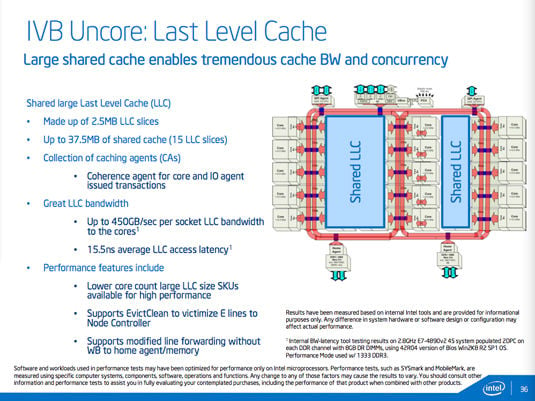

Each of the cores is co-located with a slice of up to 2.5MB of last level cache (LLC), so with a 15-core Xeon E7 v2, simple arithmetic gets you up to a hefty maximum of 37.5MB of total LLC.

However, although those cache slices may look like they're associated with their neighboring cores, they're not that limited – they form a unified, shared LLC that uses three ring busses, each synchronous with the cores' clock, with which to communicate among the cores.

Overall, the LLC system maxes out at around 450GB/sec of LLC bandwidth per socket. Not too shabby.

Intel claims that the average latency in such communication is about 15.5 nanoseconds, and Intel principal engineer Irma Esmer refined that number a bit for us, saying that latencies range from about 11ns to 20ns in the 2.8GHz part.

In addition to the 15-core, 37.5MB LLC part maxing out at a base core clock of 2.8GHz with a TDP of 155 watts, Intel is also offering a plethora of other parts, including a 15-core part running at 2.2GHz that consumes only 105W, and an HPC-targeted part that has but 12 cores, but which runs at a base clock of 3.0GHz while eating up 130W.