This article is more than 1 year old

ARM Cortex-A73: How a top-end mobe CPU was designed from scratch

RISC-taking bods branch out with new low-power, high-performance ideas

Blueprints

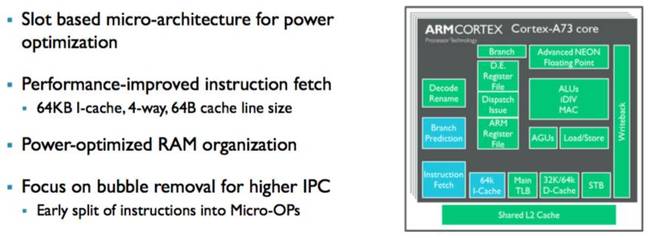

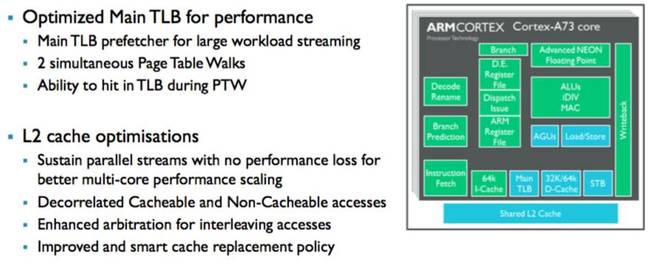

The A73's L1 instruction cache is 64KB in size (bigger than the A72's 48KB), is four-way associative, and has been tuned to save power: pipeline bubbles – little delays inserted into the pipeline to stall execution whenever instructions may clash – can be avoided by breaking instructions into micro-operations early, giving the processor's innards a better heads-up of what needs to be decoded and executed.

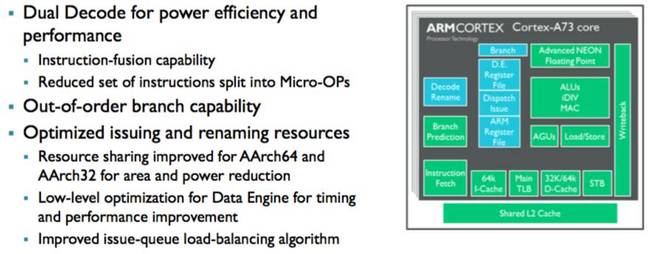

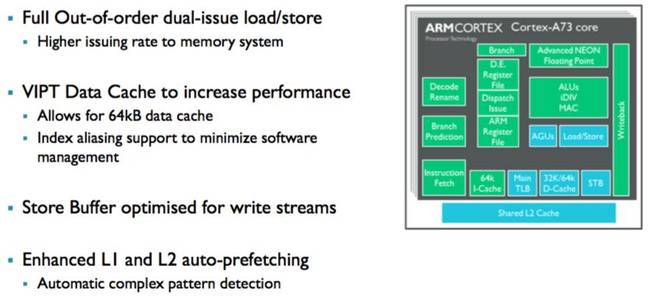

The A73 has four full out-of-order load-store units arranged as two load and two store, whereas the A72 has one load and one store unit. The decode stage can crunch most instructions in a single cycle, which is much better than the A72's three cycles, and, according to ARM, can detect common patterns of code and fuse them together, which delivers a performance boost because, well, the processor can execute them together rather than separately.

The A73's data cache is 64KB compared to the A72's 32KB. Its entries are now virtually indexed, physically tagged (VIPT), which is less power hungry and has a lower latency than the usual physically indexed, physically tagged (PIPT) cache design.

New Mali GPU

Finally, to accompany the A73 is the Mali-G71 graphics processor from ARM using its new Bifrost GPU architecture. This is designed with the Vulkan API, and virtual reality and augmented reality applications in mind. We're told it supports up to 120Hz refresh rates and 4K displays. It's an embedded GPU design, so expect it to turn up in some mobile gadgets by next year. ®

Slides provided by ARM.