This article is more than 1 year old

StoreServ's ASIC architect must have one heckuva crystal ball

Post-NAND explorations and adaptations; or, predicting future storage uses

StoreServ arrays use special hardware, an ASIC, to accelerate storage array operations, and this is redesigned for each major generation of the arrays. The current design is generation 5.

Siamak Nazari is an HPE fellow and StoreServ architect, and is heavily involved in the design of the forthcoming gen 6 ASIC.

An ASIC design has to last for five years or so once systems using it start shipping, which means Nazari has to peer into the future and discern what the characteristics of storage array media, storage array software and accessing host requirements will be between 2018, when gen 6 ASIC use is expected to start, and 2023 or so.

Nazari works with the hardware team in designing the ASIC chip. In HPE storage business organisation terms, he is part of the system-defined storage operation, headed up by Vish Mulchand, who reports in to HPE's storage head, Manish Goel.

Patrick Osbourne runs the software-defined storage section, and also reports to Goel, who reports in turn to Antonio Neri, the top man in HPE's enterprise systems business.

The gen 5 ASIC has been active during a general array evolution from pure disk and hybrid flash/disk use to all-flash designs, with consequent dramatic reduction in media access latency. Nazari assumes that there will be an evolution to post-NAND media, such as Resistive RAM (ReRAM), with Memristor being in that general category, 3D XPoint and maybe STT-RAM (Spin Transfer Torque RAM) and PCM (Phase Change Memory). The ASIC should try to be agnostic and cover the general attributes exposed by these device technologies, such as lower latency and, perhaps, byte instead of NAND's block erasability.

Nazari said that HPE sees a role for XPoint as well as ReRAM. He said the HPE-SanDisk (now WDC) partnership was ongoing, and driven by HPE's server operation. So he is seeing HPE servers (and others) using ReRAM and XPoint media with their sub-microsecond access latency when used in DIMM form. He is also expecting NVMe over Fabrics style networking with much lower network latency, which puts demands on the array to respond commensurately faster.

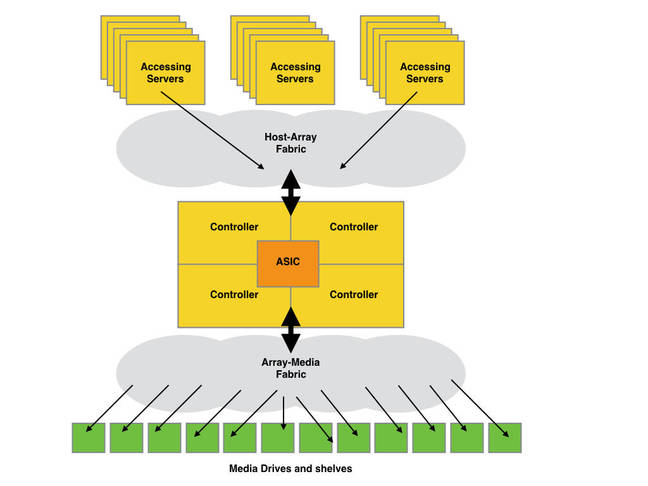

He sees the StoreServ array world having six general components; accessing server hosts, host-array fabric (typically Fibre Channel now), array controller complex with the ASIC, controller-media fabric, and the array’s media drives. Figure one shows this scheme.

He thinks the array controller-media fabric is Fibre Channel and SAS now, with a transition to NVMe fabric over the nest two to three years. Nazari is free to innovate in the ASIC area. He says it has built-in storage semantics and assumes a single system domain. An XPoint SSD will have roughly 10 microsecs latency, which compares to NVMe NAND’s 60-100 microsecs. SAS will add 10-20 microsecs to that, and has well-defined error-handling protocols, lacking in NVMe. In his view SAS latency is just fine and the protocol is more reliable than NVMe.

Figure 1. General StoreServ array scheme

Nazari aims for the gen 6 ASIC to have NVMe over fabric optimisations. He is concerned that data services such as snapshot and replication should have latencies appropriate to the gen 6 ASIC era, meaning lower. He looks at the ratio of CPU cycles to IOPS, and points out that 3PAR arrays typically use half the CPU cycles or cores needed by competing arrays because the ASIC, with an 800MB/sec bandwidth, functions like a storage co-processor.

He characterises a XEON core as having 150MB/sec bandwidth.

In the gen 5 ASIC StoreServ arrays the controllers spend a lot of time waiting for locks, and he would like to reduce that time. One way is to add more queues to the hardware, more queues than cores, and HPE us working with HBA vendors – QLogic, Emulex, LSI, etc – to add more queues to the array side of their adapter products; they are already there on the client side. This initiative is independent of specific Fibre Channel standards, such as 16Gbit/sec and 32Gbit/sec.

The whole data path between accessing servers and the media drives has to become faster and has to cope with NVMe drives and NVMe fabrics, with the ASIC helping the controllers do their job faster and better. Nazari is chasing a moving target as the NVMe over fabrics specification is evolving, and the first post-NAND drives, in the form of XPoint SSDs are expected by the end of the year, with XPoint DIMMs appearing some time in 2017.

If Nazari and his colleagues get it right then gen 6 ASIC StoreServ arrays will fit right in to a post-NAND media and NVMe fabrics era and retain their advantage over commodity arrays lacking hardware (and firmware) acceleration. This incumbent array vendor is not about to relinquish its grip on the external array business; indeed, it wants to make it tighter and the gen 6 ASIC will provide much of the power behind its teeth. ®