This article is more than 1 year old

Wisconsin badgers Apple to cough up half a billion dollars for ripping off chip designs

Uni in line for a lot of cheddar from Cook and Co

Analysis Apple has been hit with a $506m bill for infringing CPU design patents belonging to the University of Wisconsin.

Judge William Conley, of the Wisconsin Western US District Court, has ordered [PDF] the Cupertino iPhone maker to pay $506,084,992.66 (£386m) in damages. This comes after a jury found that Apple used technology in the A7 processor that was patented by the Wisconsin Alumni Research Foundation.

Apple designs its own ARM-compatible CPU cores – such as those found in the A7 system-on-chip – and uses them to power its iPhones, iPads and other gadgets.

It was determined by the courts that Cupertino's engineers had used a method for optimizing the order in which machine-code instructions are executed that researchers at Wisconsin had filed a patent for back in 1996 and been awarded in 1998. The university claimed it attempted to negotiate a license with Apple, but to no avail.

Conley's half-billion dollar payout was calculated from a combination of:

- The damages awarded by the jury.

- Supplemental damages of $1.61 for every A7 iPhone and iPad sold through October 26 2015.

- Royalties of $2.74 for every A7 sold between October 27, 2015 and December 26, 2016 (when the patent expired).

- Additional costs, plus interest through when the judgement was announced.

This bill will also accrue 0.232 per cent interest from July 1, 2017, until it is fully paid off. While nothing to sneeze at, the $506m bill is still significantly less than the maximum damages of $862m Conley had set during trial.

The decision this week stems from the 2015 jury ruling that Apple infringed on US Patent 5,781,752 with the design of the A7 chip and its handling of instructions from software.

That patent is impenetrable if you're not au fait with modern processor design but it's pretty interesting. It basically describe a speculative execution system that predicts memory dependencies within a CPU pipeline. It uses a table to track potential dependencies to avoid misspeculations, which are costly to execution speed. Specifically, it looks out for load-store pairs that can cause a misspeculation.

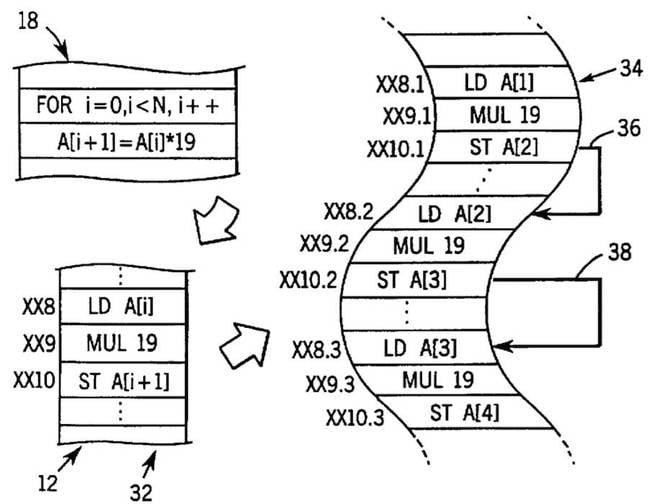

Some example C-ish pseudocode is included...

for i = 0; i < N; i++ A[i + 1] = A[i] * 19

...the main body of which is compiled into this imaginary CPU instruction code...

LOAD A(i) MUL 19 STORE A(i+1)

The uni's designs describe how to efficiently handle code like this. The register A is filled with a value from memory at location i, the value is multiplied by 19, and the result stored in the word next to location i in memory.

The problem is, in a complex pipelined out-of-order processor, you can't speculatively load data into A for the next loop iteration while you're still working on the current iteration because whatever will be loaded into A in the next iteration will be affected by the store in the current iteration. So a table is used to keep track of these load-store pairings to avoid failed speculations.

This example is illustrated in the patent, and we've included the diagram below.

As you can see, the store in one iteration of the loop affects the load in the next iteration; any speculative execution of that load will have to be dumped if it uses out-of-date information. Obviously, Intel and other designers of out-of-order processors have their own ways of dealing with this conflict, or have licensed the tech from the university. In any case, a court has found Apple's solution was too similar to the above approach, hence this week's nine-figure bill.

The A7 chip was used by Apple in the iPhone 5S, iPad Air, Mini 2 and Mini 3. It has since been succeeded by the A8 and A9, which were not subject to this patent claim. Apple did not respond to a request for comment on the matter. ®

Patent analysis by Chris Williams.