This article is more than 1 year old

Intel shows how chiplets will form Meteor Lake CPUs

Different core counts, different cache sizes, and various cores possible in mix and match design, it says

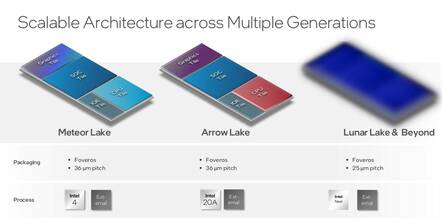

Hot Chips Intel has given more detail on how its upcoming Meteor Lake processors will be made from multiple chiplets, enabling it to mix and match to deliver different capabilities, and easing the introduction of its successor, Arrow Lake – which follows the same construction.

At the Hot Chips conference, the chipmaker presented a session on how its upcoming CPUs will be stitched together using its Foveros packaging technology to build what is expected to be its 14th Gen Core processors.

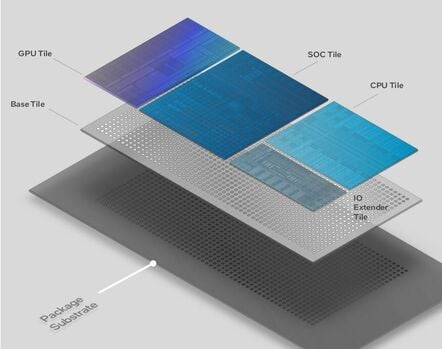

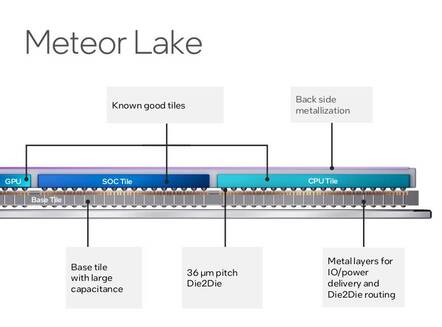

Inside the chip package, Meteor Lake will be composed of four different interconnected tiles, comprising a CPU tile, graphics tile, SoC tile and an I/O extender tile, all mounted on a fifth base tile.

“Our goal was to get disaggregation benefits not achievable with monolithic design, but all the while keeping disaggregation taxes to a minimum,” said senior principal engineer Slade Morgan.

“We have a disaggregated core tile, we have a disaggregated graphics tile, and by the way, graphics has very different performance characteristics for media and display. So we separated those out.”

Earlier rumors had indicated that the graphics tile might be manufactured for Intel by TSMC using a different process node to the compute tile. Such a possibility was hinted at by CEO Pat Gelsinger in his earlier keynote speech, but the company did not disclose that in this session.

According to Morgan, this architecture allows for different core tiles in the Meteor Lake family to feature different core counts, different cache sizes, or mixes of performance and efficient cores, “and we have the ability to flexibly and easily target each segment without disrupting the rest of the design,” he said.

- Apple and Intel likely the first to use TSMC's 2nm node in 2025

- Intel's Gelsinger talks up 'systems foundry' era of trillion-transistor chips

- Intel turns to private equity to help pay for new factories

- Intel set to squeeze the flops out of Ponte Vecchio GPU

Over the life of the Meteor Lake family, new iterations of the core will become available and new process nodes will become available, and these can be incorporated as soon as they are ready, Morgan claimed. The core tile in the initial Meteor Lake chips is expected to be a 7nm chiplet manufactured with the Intel 4 process node.

Graphics is scalable in the same way, with Morgan stating that the goal is to scale graphics performance from very low power mobile configurations all the way up to performance equivalent to a discrete GPU.

The SoC tile has functions such as the memory controller and I/O fabric and is designed to focus on low power operation, while the I/O extender tile can be offered in different versions to provide a different mix of I/O for different segments. The base tile provides the power and interconnections between other tiles, rather like a motherboard.

The successor to Meteor Lake will be Arrow Lake, and Intel said that this will follow the same architecture, but that the core tile will be a new design manufactured using the Intel 20A process node and it will also bring in new graphics tile options.

Beyond Arrow Lake is Lunar Lake, and this will continue the theme, but moves to the next iteration of the Foveros packaging technology with a 25µm bump pitch rather than the 36µm bump pitch used for Meteor Lake.

Intel said that Meteor Lake chips have been booted up and are working in the company's labs, which should mean that the chips will arrive in 2023 as expected followed by Arrow Lake in 2024, as long as there are no further issues with the process nodes, of course. ®